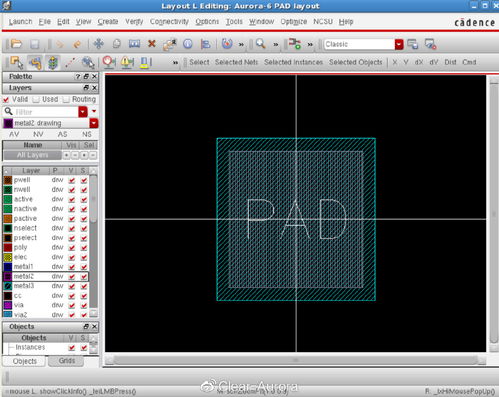

集成電路CAD設(shè)計(jì)中的芯片焊盤(pán)與版圖布局設(shè)計(jì)

集成電路設(shè)計(jì)是現(xiàn)代電子技術(shù)的核心領(lǐng)域之一,其中CAD(計(jì)算機(jī)輔助設(shè)計(jì))工具的應(yīng)用極大地提升了設(shè)計(jì)效率與精確度。在集成電路設(shè)計(jì)中,芯片焊盤(pán)與版圖布局設(shè)計(jì)是尤為關(guān)鍵的環(huán)節(jié),它們直接影響芯片的性能、可靠性和制造成本。

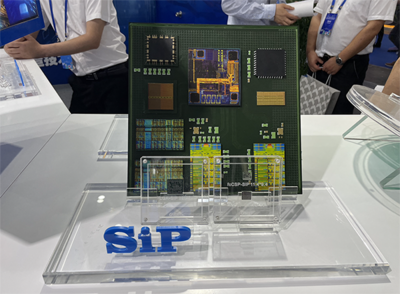

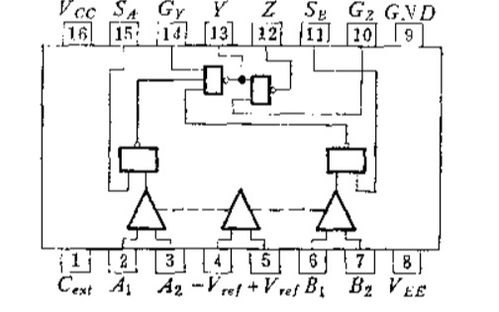

芯片焊盤(pán)設(shè)計(jì)是集成電路與外部電路連接的橋梁。焊盤(pán)通常位于芯片的邊緣,負(fù)責(zé)將內(nèi)部電路信號(hào)引出,并通過(guò)鍵合線或倒裝焊技術(shù)與封裝基板相連。設(shè)計(jì)時(shí)需考慮焊盤(pán)尺寸、間距、材料及電流承載能力。例如,電源焊盤(pán)需足夠大以承受高電流,而信號(hào)焊盤(pán)則需優(yōu)化布局以減少串?dāng)_。焊盤(pán)的排列應(yīng)遵循封裝工藝的要求,確保鍵合過(guò)程中的機(jī)械穩(wěn)定性。

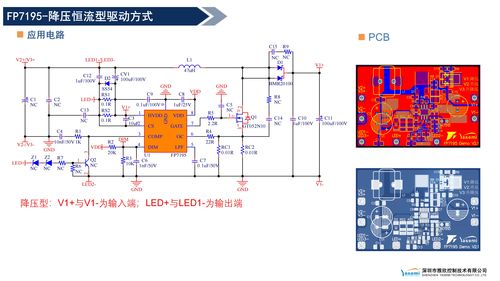

版圖布局設(shè)計(jì)則是將電路邏輯轉(zhuǎn)化為物理結(jié)構(gòu)的過(guò)程,涉及晶體管、電阻、電容等元件的放置與互連。設(shè)計(jì)目標(biāo)包括最小化芯片面積、優(yōu)化信號(hào)路徑、降低功耗和增強(qiáng)抗干擾能力。CAD工具如Cadence或Synopsys提供了自動(dòng)化布局布線功能,但設(shè)計(jì)師仍需手動(dòng)調(diào)整關(guān)鍵部分。例如,模擬電路部分需隔離噪聲,高頻電路需縮短互連長(zhǎng)度以減少延遲。布局時(shí)還需考慮制造工藝的約束,如最小線寬、間距規(guī)則,以及熱管理和電源分布均勻性。

在實(shí)際設(shè)計(jì)中,焊盤(pán)與版圖布局需協(xié)同優(yōu)化。焊盤(pán)的位置影響版圖的整體規(guī)劃,而版圖的密度和布線復(fù)雜度又反過(guò)來(lái)制約焊盤(pán)布局。通過(guò)迭代仿真和驗(yàn)證,設(shè)計(jì)師可以確保設(shè)計(jì)滿足電氣特性和可靠性標(biāo)準(zhǔn)。隨著集成電路工藝向納米級(jí)發(fā)展,焊盤(pán)和版圖設(shè)計(jì)面臨更多挑戰(zhàn),如寄生效應(yīng)、信號(hào)完整性和熱效應(yīng),這要求設(shè)計(jì)師具備深厚的專業(yè)知識(shí)并借助先進(jìn)CAD工具。

芯片焊盤(pán)與版圖布局設(shè)計(jì)是集成電路CAD設(shè)計(jì)中的精髓,它們不僅決定了芯片的功能實(shí)現(xiàn),還影響著最終產(chǎn)品的性能與成本。通過(guò)精細(xì)的設(shè)計(jì)與驗(yàn)證,可以打造出高效、可靠的集成電路產(chǎn)品,推動(dòng)電子技術(shù)的持續(xù)創(chuàng)新。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.cenh.cn/product/28.html

更新時(shí)間:2026-04-14 20:27:59